#### **Up and Down the Stack!**

#### What we did before the break...

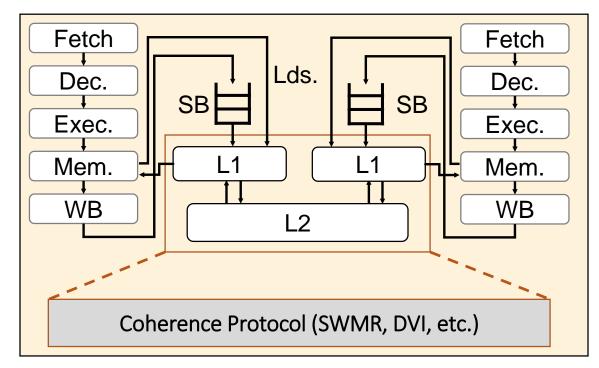

Microarchitecture

#### SC/TSO/RISC-V MCM?

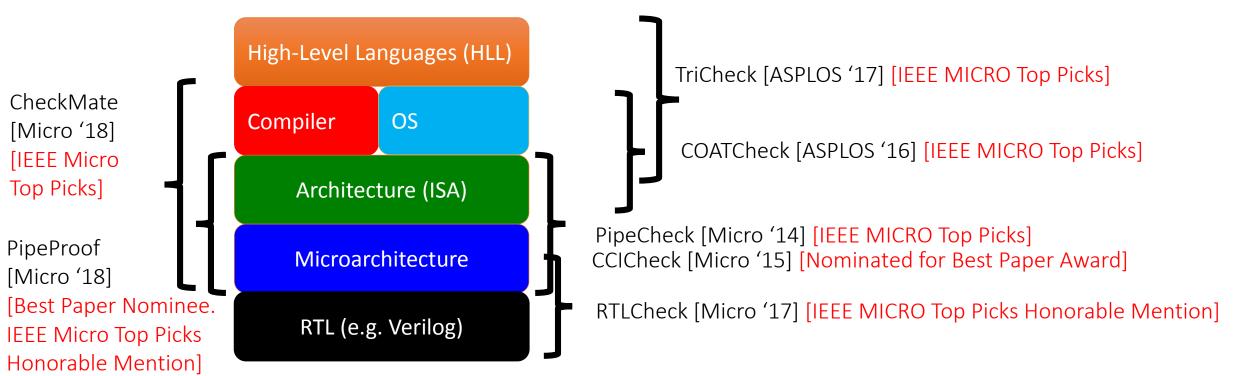

# The Check Suite: Tools For Verifying Memory Orderings and their Security Implications

# The Check Suite: Tools For Verifying Memory Orderings and their Security Implications

For more info: check.cs.Princeton.edu

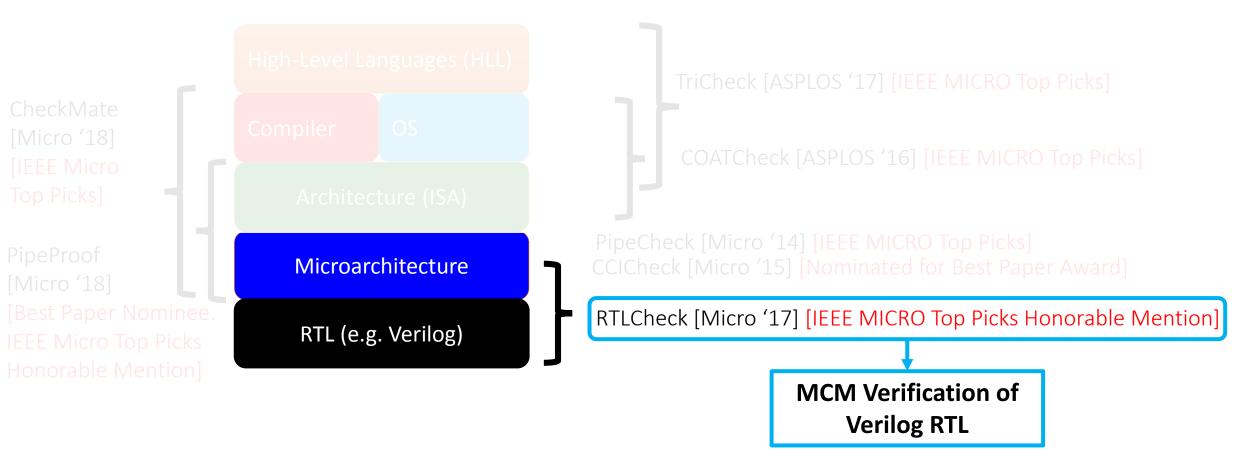

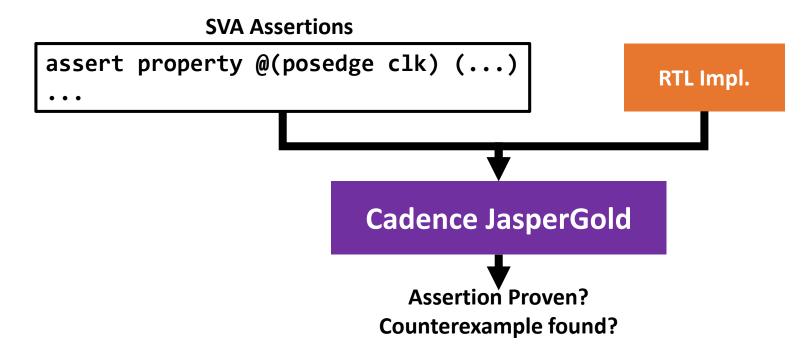

### What if I want to verify RTL (Verilog)?

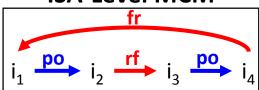

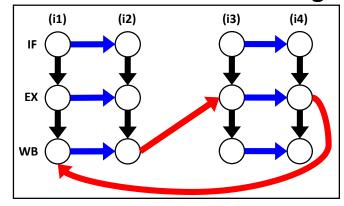

#### **ISA-Level MCM**

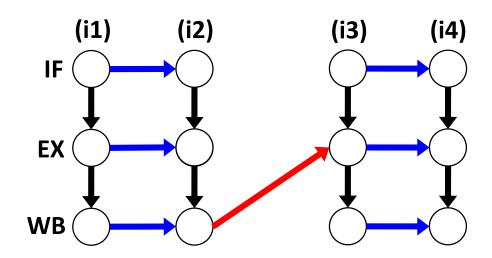

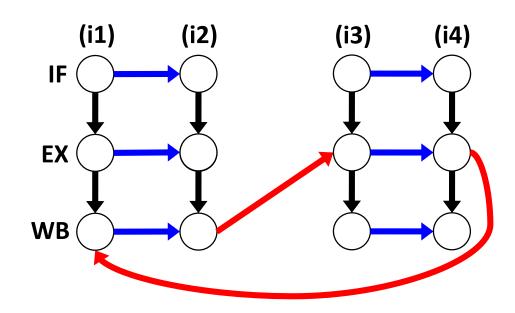

#### **Microarchitectural Orderings**

```

acyclic (po U co U rf U fr)

```

```

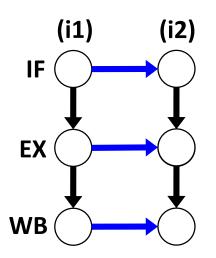

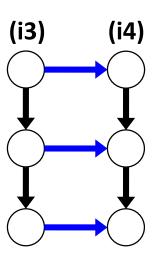

Axiom "PO_Fetch":

forall microop "i1", "i2",

SameCore i1 i2 /\ ProgramOrder i1 i2 =>

AddEdge ((i1, IF), (i2, IF)).

```

Verified with PipeProof

### What if I want to verify RTL (Verilog)?

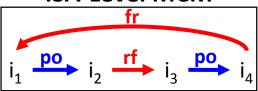

#### **ISA-Level MCM**

#### **Microarchitectural Orderings**

acyclic (po U co U rf U fr)

```

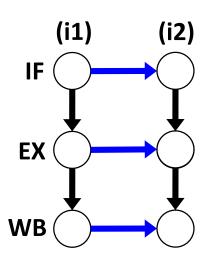

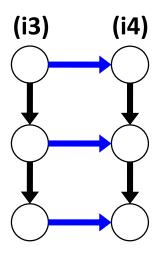

Axiom "PO_Fetch":

forall microop "i1", "i2",

SameCore i1 i2 /\ ProgramOrder i1 i2 =>

AddEdge ((i1, IF), (i2, IF)).

```

Verified with PipeProof

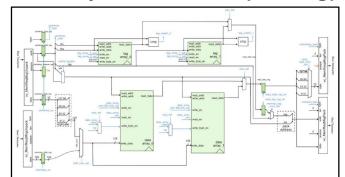

#### RTL implementation (Verilog)

[RTL Image: Christopher Batten]

### What if I want to verify RTL (Verilog)?

#### **ISA-Level MCM**

#### **Microarchitectural Orderings**

acyclic (po U co U rf U fr)

Axiom "PO\_Fetch": forall microop "i1", "i2", SameCore i1 i2 /\ ProgramOrder i1 i2 => AddEdge ((i1, IF), (i2, IF)).

Verified with PipeProof

#### **RTL** implementation (Verilog)

[RTL Image: Christopher Batten]

...but usually ignores memory consistency!

...but usually ignores memory consistency!

ISA-Formal [Reid et al. CAV 2016]

-Instr. Operational Semantics

No MCM verification!

...but usually ignores memory consistency!

ISA-Formal [Reid et al. CAV 2016]

-Instr. Operational Semantics

No MCM verification!

DOGReL [Stewart et al. DIFTS 2014]

-Memory subsystem transactions

No multicore MCM verification!

...but usually ignores memory consistency!

ISA-Formal [Reid et al. CAV 2016]

-Instr. Operational Semantics

No MCM verification!

DOGReL [Stewart et al. DIFTS 2014]

-Memory subsystem transactions

No multicore MCM verification!

Kami

[Vijayaraghavan et al. CAV 2015] [Choi et al. ICFP 2017]

-MCM correctness for all programs, but...

Needs Bluespec design and manual proofs!

...but usually ignores memory consistency!

# Lack of automated memory

## consistency verification at RTL!

[Vijayaraghavan et al. CAV 2015] [Choi et al. ICFP 2017]

-MCM correctness for all programs, but...

Needs Bluespec design and manual proofs!

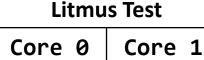

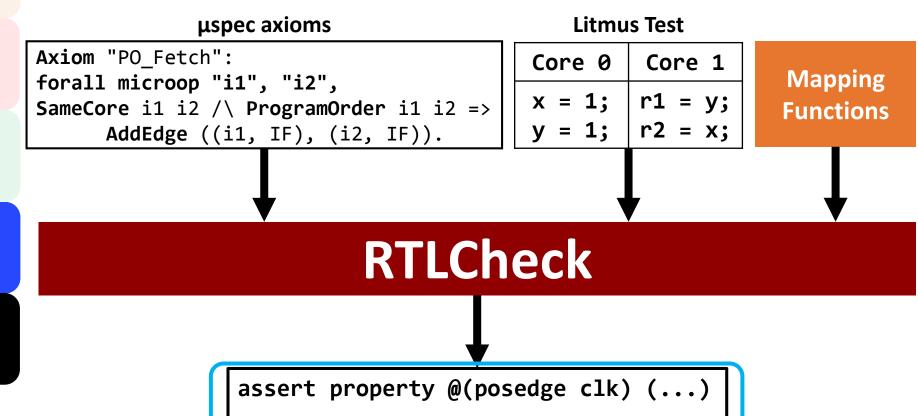

### RTLCheck: Checking RTL Consistency Orderings

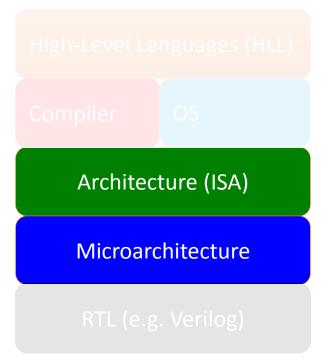

High-Level Languages (HLL)

Compile

Instruction Set (ISA

Microarchitecture

Processor RTL (Verilog)

■ RTLCheck enables automated checking of Verilog RTL against µspec axioms for litmus test suites

| Core 0 | core 1  |

|--------|---------|

| x = 1; | r1 = y; |

| y = 1; | r2 = x; |

**Mapping Functions**

RTLCheck

assert property @(posedge clk) (...)

**Test-specific Temporal RTL Properties**

### RTLCheck: Checking RTL Consistency Orderings

High-Level Languages (HLL)

Compile

Instruction Set (ISA

Microarchitecture

Processor RTL (Verilog)

■ RTLCheck enables automated checking of Verilog RTL against µspec axioms for litmus test suites

Test-specific Temporal RTL Properties

### System Verilog Assertions (SVA)

- SVA: Industry standard for RTL verification, e.g.: ARM [Reid et al. CAV 2016]

- Based on Linear Temporal Logic (LTL) with regular operators

- Commercial tools (e.g. JasperGold) can formally verify SVA assertions

- Translating µspec to SVA => RTL MCM verification using industry flows

- But it's not that simple!

### Meaning can be Lost in Translation!

小心地滑

### Meaning can be Lost in Translation!

## 小心地滑

(Caution: Slippery Floor)

#### Meaning can be Lost in Translation!

小心地滑

(Caution: Slippery Floor)

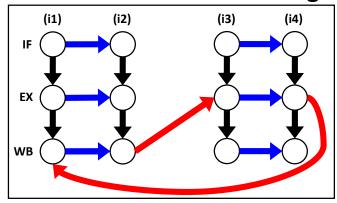

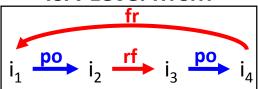

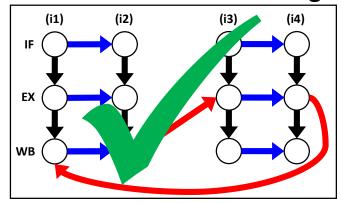

<u>Axiomatic</u> Microarch. Verification

Execution examined as

a single unit (graph)

Axiomatic Microarch. Verification

Execution examined as

a single unit (graph)

Temporal

RTL Verification

(SVA, etc)

Execution examined cycle by cycle

<u>Axiomatic</u> Microarch. Verification

Execution examined as

a single unit (graph)

#### µspec/SVA Mismatch!

Temporal

RTL Verification

(SVA, etc)

Execution examined cycle by cycle

- Tricky to translate µspec to SVA while maintaining µspec semantics

- SVA Verifiers (JasperGold) don't implement full SVA spec!

- Causes further complications

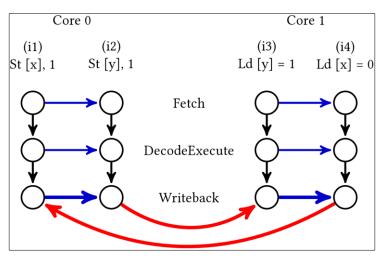

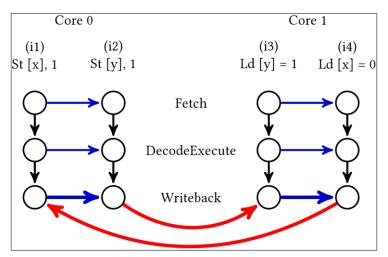

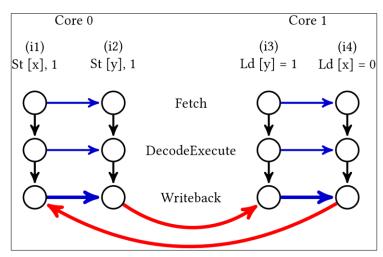

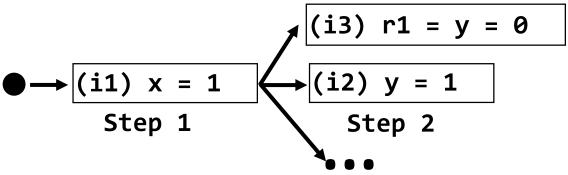

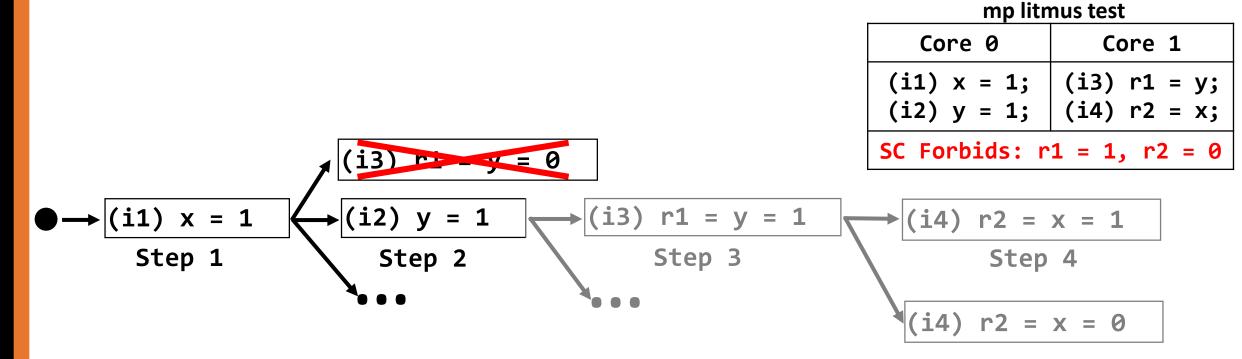

- Example: Outcome Filtering

- Filtering litmus test executions to those that have particular values for loads

- In this case, outcome filtering is **easy and efficient**

- Always know what the load values are

- Can draw (red) edges based on these values

| Core 0                     | Core 1                       |

|----------------------------|------------------------------|

| (i1) x = 1;<br>(i2) y = 1; | (i3) r1 = y;<br>(i4) r2 = x; |

|                            |                              |

- In this case, outcome filtering is **easy and efficient**

- Always know what the load values are

- Can draw (red) edges based on these values

| inp intinus test           |                              |

|----------------------------|------------------------------|

| Core 0                     | Core 1                       |

| (i1) x = 1;<br>(i2) y = 1; | (i3) r1 = y;<br>(i4) r2 = x; |

| SC Forbids: r1 = 1, r2 = 0 |                              |

- In this case, outcome filtering is **easy and efficient**

- Always know what the load values are

- Can draw (red) edges based on these values

| Core 0                          | Core 1                       |

|---------------------------------|------------------------------|

| (i1) x = 1;                     | (i3) r1 = y;<br>(i4) r2 = x; |

| (12) $y - 1$                    | (14) 12 - X,                 |

| SC Forbids: $r1 = 1$ , $r2 = 0$ |                              |

- In this case, outcome filtering is **easy and efficient**

- Always know what the load values are

- Can draw (red) edges based on these values

| Core 0                     | Core 1                       |

|----------------------------|------------------------------|

| (i1) x = 1;                | (i3) r1 = y;<br>(i4) r2 = x; |

| (i2) y = 1;                | (i4) r2 = x;                 |

| SC Forbids: r1 = 1, r2 = 0 |                              |

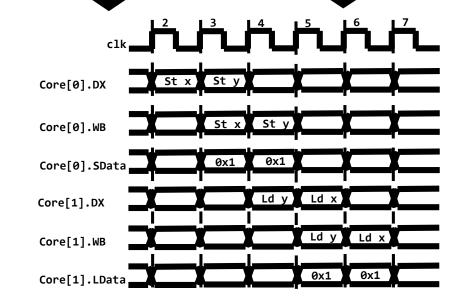

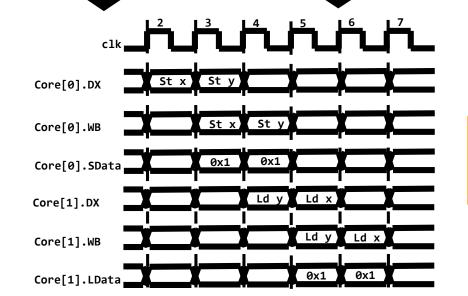

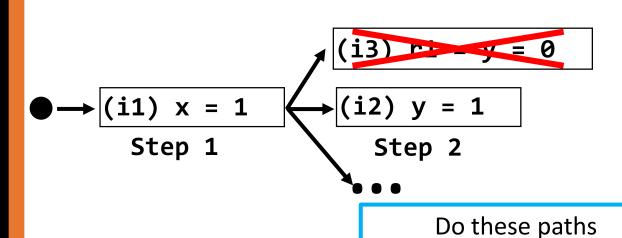

- Don't know load values until the end of the execution!

- Must look into future to ensure we're checking the right executions

| inp intinus test           |                              |

|----------------------------|------------------------------|

| Core 0                     | Core 1                       |

| (i1) x = 1;<br>(i2) y = 1; | (i3) r1 = y;<br>(i4) r2 = x; |

| SC Forbids: r1 = 1, r2 = 0 |                              |

- Don't know load values until the end of the execution!

- Must look into future to ensure we're checking the right executions

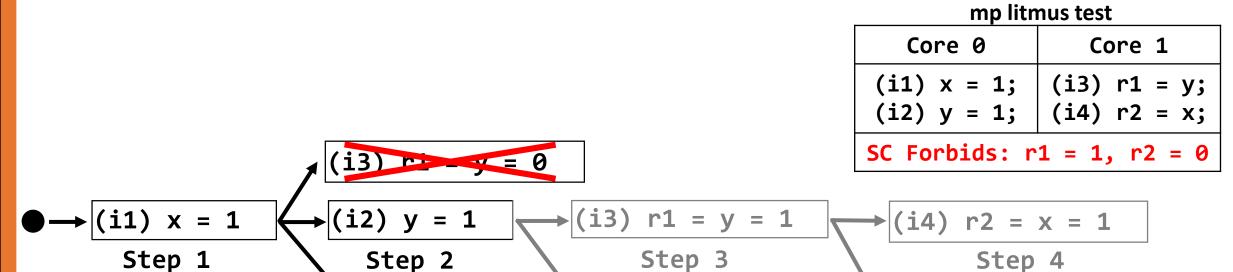

mp litmus test

| Core 0                          | Core 1                       |

|---------------------------------|------------------------------|

| (i1) x = 1;<br>(i2) y = 1;      | (i3) r1 = y;<br>(i4) r2 = x; |

| SC Forbids: $r1 = 1$ , $r2 = 0$ |                              |

Does this path correspond to r1=1, r2=0?

Need to look into future!

- Don't know load values until the end of the execution!

- Must look into future to ensure we're checking the right executions

| Core 0                          | Core 1                       |

|---------------------------------|------------------------------|

| (i1) x = 1;<br>(i2) y = 1;      | (i3) r1 = y;<br>(i4) r2 = x; |

| SC Forbids: $r1 = 1$ , $r2 = 0$ |                              |

Step 1 Step 2

$$(i3)$$

r1 = y = 1  $(i4)$  r2 = x =

- Don't know load values until the end of the execution!

- Must look into future to ensure we're checking the right executions

mp litmus test

| Core 0                          | Core 1                       |

|---------------------------------|------------------------------|

| (i1) x = 1;<br>(i2) y = 1;      | (i3) r1 = y;<br>(i4) r2 = x; |

| SC Forbids: $r1 = 1$ , $r2 = 0$ |                              |

$$(i1) x = 1$$

$$Step 1$$

$$(i2) y = 1$$

$$Step 2$$

$$(i3) r1 = y = 1$$

$$Step 3$$

$$(i4) r2 = x = 1$$

$$(i4) r2 = x = 0$$

r2 can return 0? Carry on to step 2.

- Don't know load values until the end of the execution!

- Must look into future to ensure we're checking the right executions

Do these paths correspond to r1=1,r2=0?

Look into future again!

(i4) r2 = x;

SC Forbids: r1 = 1, r2 = 0

Don't know load values until the end of the execution!

correspond to r1=1,r2=0?

Look into future again!

■ Must look into future to ensure we're checking the right executions

- Don't know load values until the end of the execution!

- Must look into future to ensure we're checking the right executions

- Don't know load values until the end of the execution!

- Must look into future to ensure we're checking the right executions

Looking into future => **expensive** liveness analysis!

SVA Verifiers **approximate** by only checking upto current step!

Makes **outcome filtering impossible\*** to do!

0

#### Solution: Load Value Constraints

Core 0 Core 1

(i1) x = 1; (i3) r1 = y;

(i2) y = 1; (i4) r2 = x;

SC Forbids: r1 = 1, r2 = 0

mp

- Don't filter based on outcome

- Translate **all** possible outcomes

- Tag each case with appropriate load value constraints

- reflect the data constraints required for edge(s)

- Ongoing work: Precisely formalise the µspec/SVA mismatch

- How much is fundamental? How much is due to SVA verifier approximation?

#### Axiom "Read\_Values":

Every load either reads **BeforeAllWrites OR** reads **FromLatestWrite**

#### Property to check:

$| mapNode(Ld x \rightarrow St x, Ld x == 0) or mapNode(St x \rightarrow Ld x, Ld x == 1);$

#### Solution: Load Value Constraints

- Don't filter based on outcome

- Translate **all** possible outcomes

- Tag each case with appropriate load value constraints

- reflect the data constraints required for edge(s)

- Ongoing work: Precisely formalise the µspec/SVA mismatch

- How much is fundamental? How much is due to SVA verifier approximation?

```

Axiom "Read_Values":

```

Every load either reads BeforeAllWrites OR reads FromLatestWrite

#### Property to check:

mapNode(Ld  $x \rightarrow St x$ , Ld x == 0) or mapNode(St  $x \rightarrow Ld x$ , Ld x == 1);

#### Solution: Load Value Constraints

- Don't filter based on outcome

- Translate <u>all</u> possible outcomes

- Tag each case with appropriate load value constraints

- reflect the data constraints required for edge(s)

- Ongoing work: Precisely formalise the µspec/SVA mismatch

- How much is fundamental? How much is due to SVA verifier approximation?

#### Axiom "Read\_Values":

Every load either reads <a href="BeforeAllWrites">BeforeAllWrites</a> OR reads <a href="FromLatestWrite">FromLatestWrite</a>

#### Property to check:

mapNode(Ld  $x \rightarrow St x$ , Ld x == 0) or mapNode(St  $x \rightarrow Ld x$ , Ld x == 1)

#### Solution: Load Value Constraints

- Don't filter based on outcome

- Translate **all** possible outcomes

- Tag each case with appropriate load value constraints

- reflect the data constraints required for edge(s)

- Ongoing work: Precisely formalise the µspec/SVA mismatch

- How much is fundamental? How much is due to SVA verifier approximation?

```

Axiom "Read_Values":

```

Every load either reads <a href="BeforeAllWrites">BeforeAllWrites</a> OR reads <a href="FromLatestWrite">FromLatestWrite</a>

#### Property to check:

mapNode(Ld  $x \rightarrow St x$ , Ld x == 0) or mapNode(St  $x \rightarrow Ld x$ , Ld x == 1);

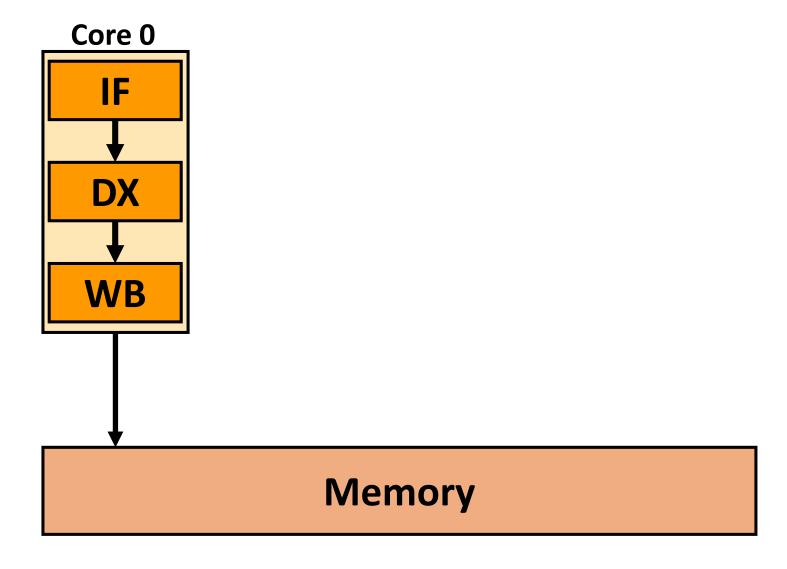

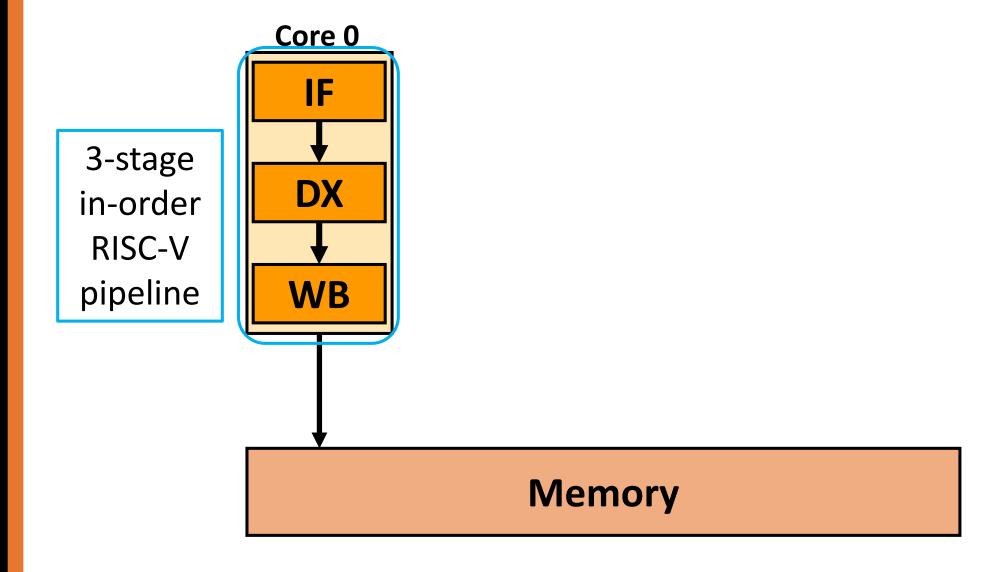

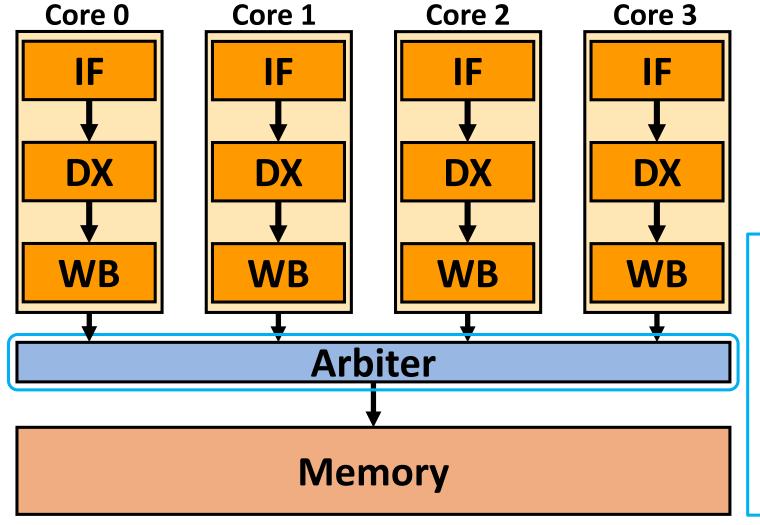

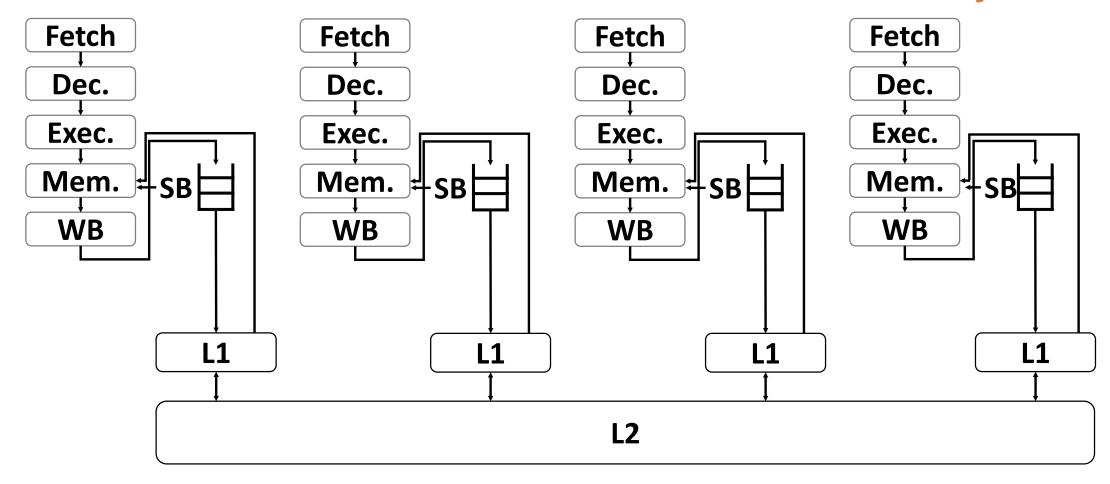

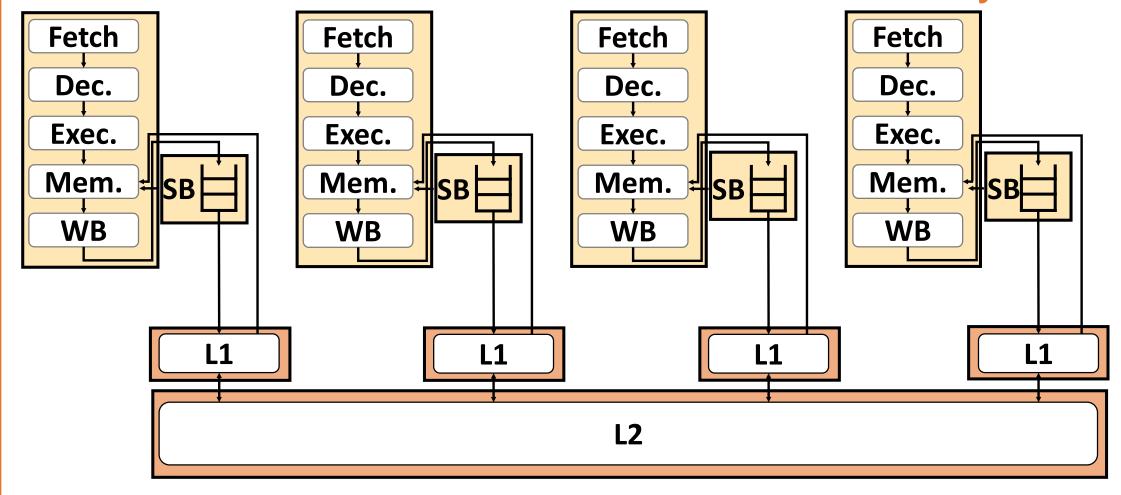

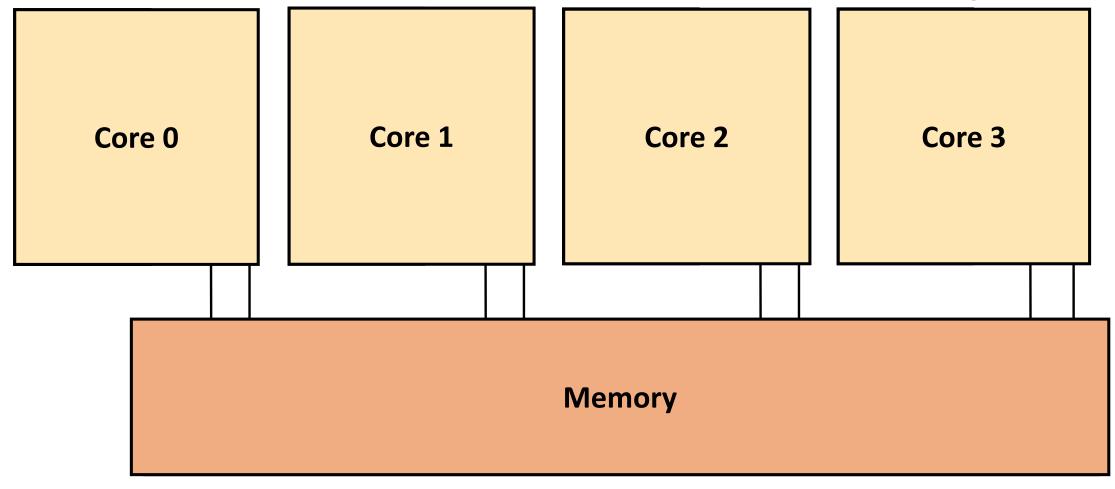

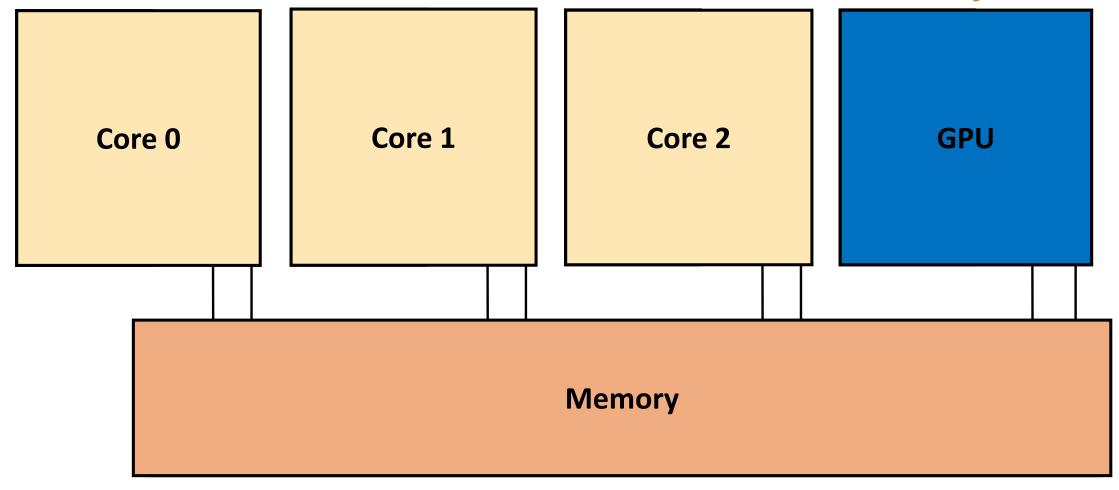

# Multi-V-scale: a Multicore Case Study

# Multi-V-scale: a Multicore Case Study

#### Multi-V-scale: a Multicore Case Study

Arbiter enforces that only one core can access memory at any time

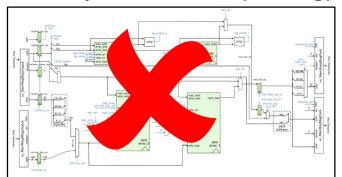

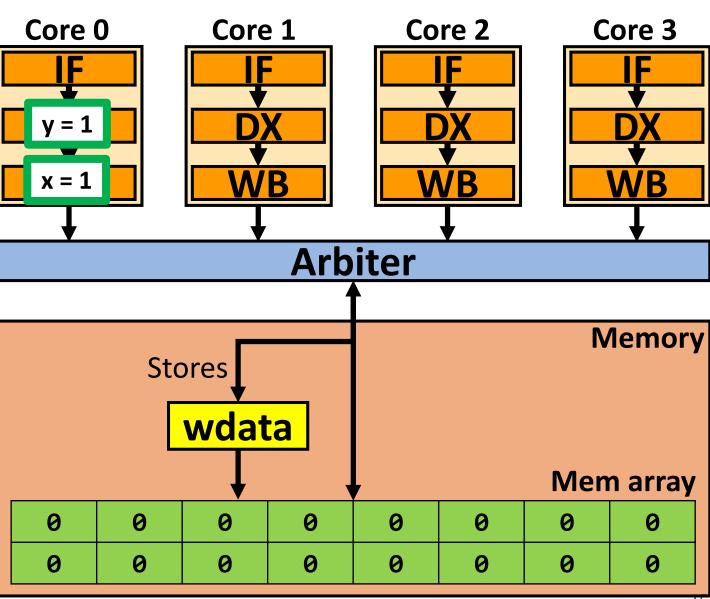

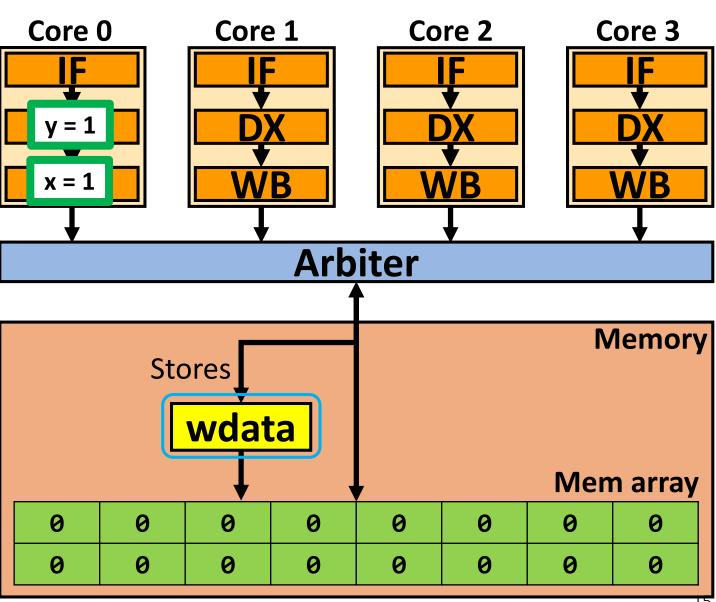

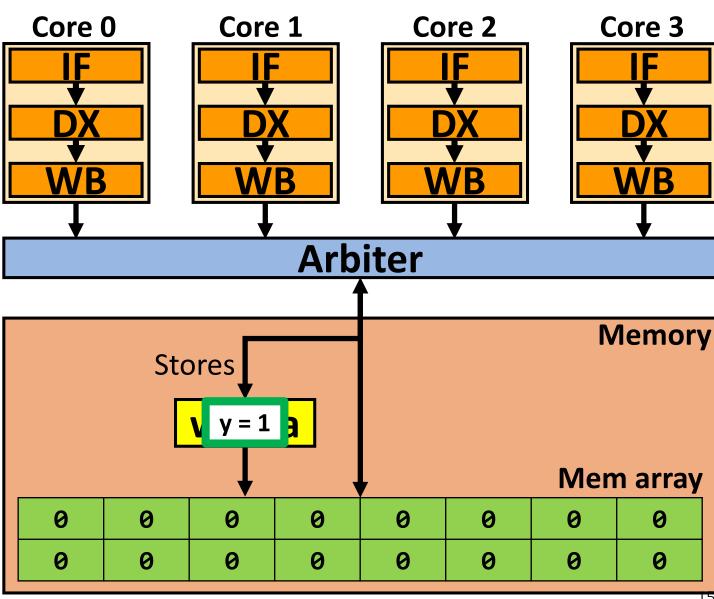

## Bug Discovered in V-scale Mem. Implementation

- When two stores are sent to memory in successive cycles, first of two stores is <u>dropped</u> by memory!

- Bug would occur even in single-core V-scale

- Fixed bug by eliminating intermediate wdata reg

## Bug Discovered in V-scale Mem. Implementation

- When two stores are sent to memory in successive cycles, first of two stores is <u>dropped</u> by memory!

- Bug would occur even in single-core V-scale

- Fixed bug by eliminating intermediate wdata reg

## Bug Discovered in V-scale Mem. Implementation

- When two stores are sent to memory in successive cycles, first of two stores is dropped by memory!

- Bug would occur even in single-core V-scale

- Fixed bug by eliminating intermediate wdata reg

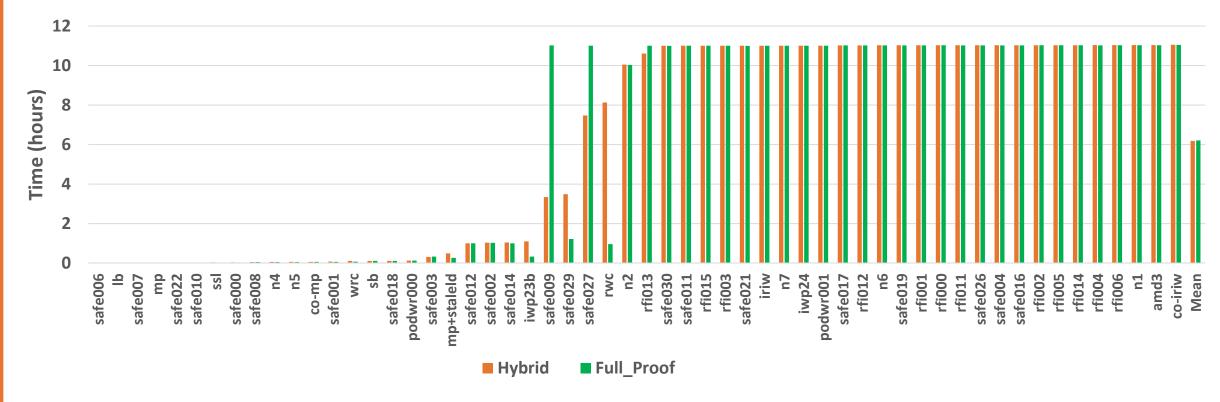

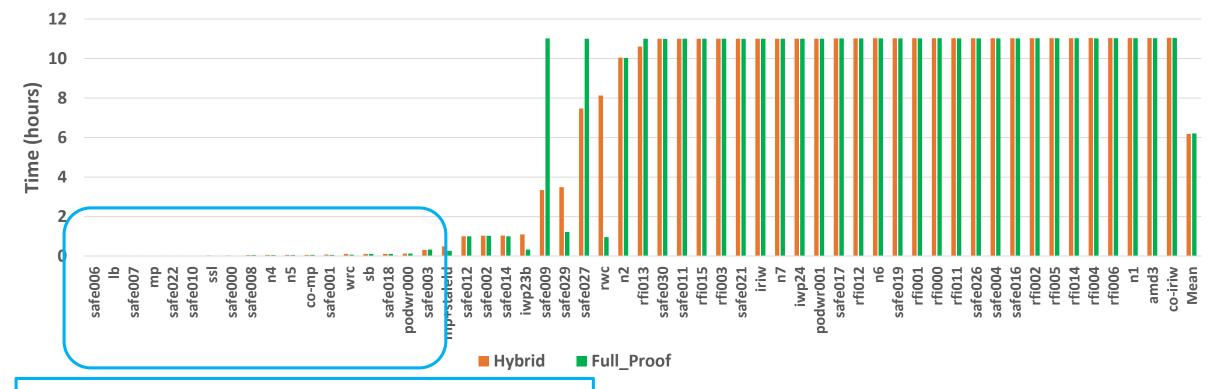

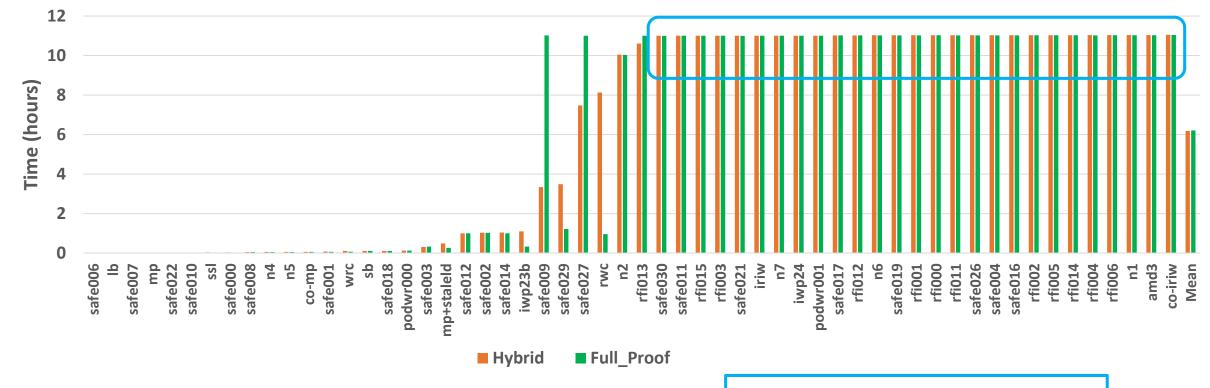

## Results: Time to Prove Properties

■ Two configurations (**Hybrid** and **Full\_Proof**), avg. runtime 6.2 hrs

#### Results: Time to Prove Properties

■ Two configurations (**Hybrid** and **Full\_Proof**), avg. runtime 6.2 hrs

Complete quickly when JasperGold detects that **litmus test outcome can never occur**

## Results: Time to Prove Properties

■ Two configurations (**Hybrid** and **Full\_Proof**), avg. runtime 6.2 hrs

Max runtime 11 hours (if some properties unproven)

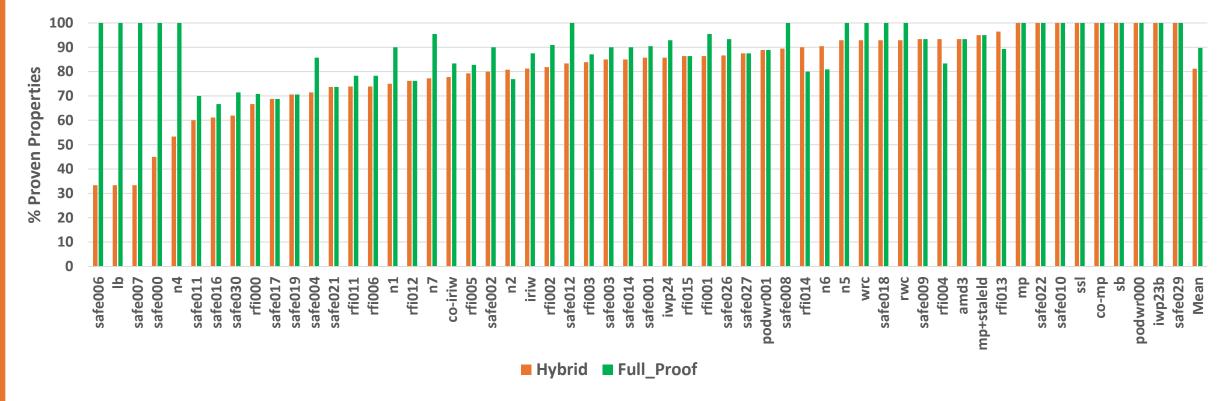

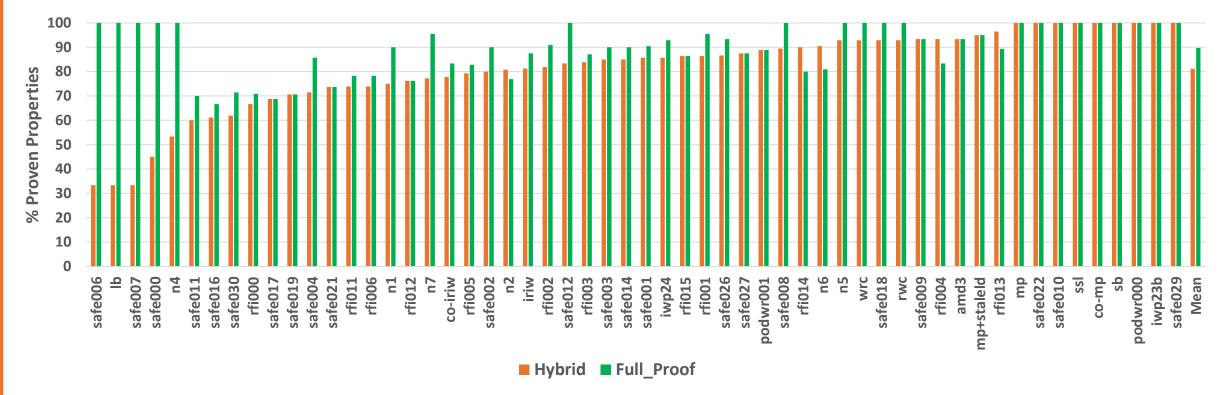

#### Results: Percentage of Proven Properties

■ Full\_Proof config generally better (90%/test) than Hybrid (81%/test)

#### Results: Percentage of Proven Properties

■ Full\_Proof config generally better (90%/test) than Hybrid (81%/test)

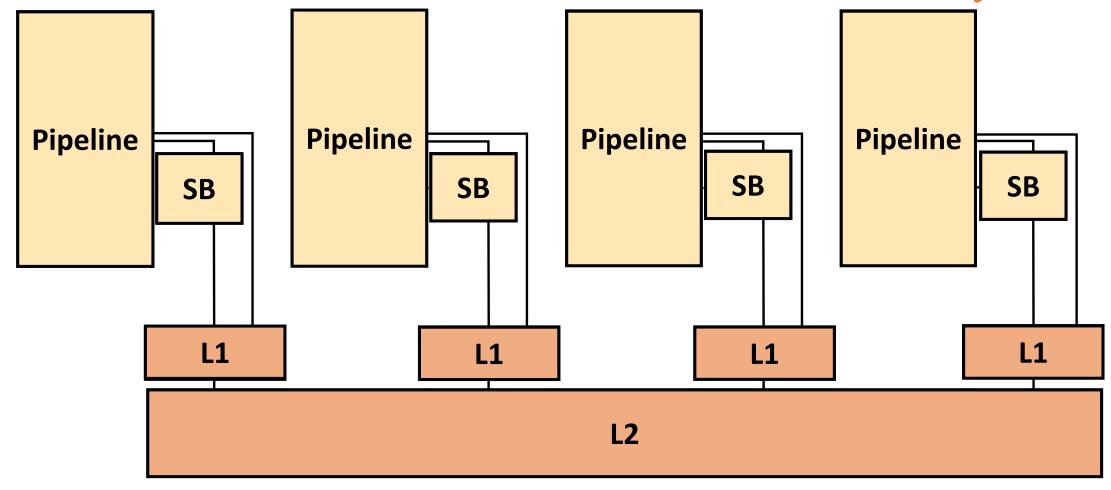

What about larger designs?

- Verify modules, compose together hierarchically

- Great for early-stage verification!

- Improved scalability and handling of heterogeneity

- Verify modules, compose together hierarchically

- Great for early-stage verification!

- Improved scalability and handling of heterogeneity

- Verify modules, compose together hierarchically

- Great for early-stage verification!

- Improved scalability and handling of heterogeneity

- Verify modules, compose together hierarchically

- Great for early-stage verification!

- Improved scalability and handling of heterogeneity

- Verify modules, compose together hierarchically

- Great for early-stage verification!

- Improved scalability and handling of heterogeneity

#### RTLCheck Takeaways

- First automated RTL MCM verification for litmus test suites

- Engineers can check MCM properties of their RTL themselves

- Compatible with existing industry flows and tools

- Novel algorithms to translate **µspec** axioms to temporal **SVA** properties

- Discovered bug in memory implementation of RISC-V V-scale processor

- Open-source and available at <a href="https://github.com/ymanerka/rtlcheck">https://github.com/ymanerka/rtlcheck</a>

- Ongoing Work: Modular MCM Verification for Scalable Analysis

- Accolades:

- "Honorable Mention" from 2017 Top Picks of Comp. Arch. Conferences